[nextpage title=”The 64-bit Xeon Processor”]

One month ago Intel officially released their last processor that hadn’t a 64-bit version: Xeon XP. Xeon MP is a processor target to multiprocessor servers with four or more CPUs, based on Pentium 4 microarchitecture.

This new Xeon MP model is also known by its code-name Truland and Intel also has released a new chipset for it, Intel E8500. This new CPU has some new features if compared to the previous Xeon MP model:

- Clocks from 2.83 GHz to 3.66 GHz.

- EM64T technology, allowing memory addressing up to 1 TB (it uses a 40-bit address bus). Due to limitations on the memory modules found on the market today, this CPU is limited to 64 GB of DDR2-400 memory. However, with the FB-DIMM memory release this limit will probably increase.

- 667 MHz external bus.

- 1 MB L2 memory cache.

- L3 memory cache up to 8 MB (the exact quantity depends on the model). This memory is locate on the processor’s body, but not in its core (die), but in a silicon chip located besides the processor silicon piece, accessed at 1,066 MHz.

- xD (Execute Disable) bit, blocking virus from being executed (click here to learn more about this technology).

- DBS (Demand Based Switching), a feature based on the SpeedStep technology. This feature allows the server’s processors to reduce their clock rate depending on the server load, thus saving energy. For example, if the server is used as a web server, if the traffic drops a lot in the middle of the night , the server will automatically reduce the clock rate of the processors. The saved energy may not seem a lot, but think about a data center with hundreds of server. In this scenario the savings on the electricity bill can be important.

- RAS (Reliability, Accessibility and Support): Xeon and Xeon MP CPUs allow “memory sparing” and “memory mirroring” techniques, which are also known as “memory RAID”. With the first technology, if the processor finds a defective memory module, it automatically disables that module. This technology goes deeper, allowing the CPU to turn off only the exact memory chip that is defective. With memory mirroring the data available at one memory module is replicated to another memory module in real time. If one of the memory modules goes defective, the backup module is still running and there is no data loss. Xeon MP, contrary to the “plain” Xeon, allows memory module replacement with the server up and running (“hot swap”). With Xeon processor it is necessary to turn the server off before replacing the memory modules.

- Enhanced Defer Bus Protocol: Allows one processor to forward tasks to another processor on the system, feature not available on the “plain” Xeon.

- Virtualization technology: This new processor and the new Intel E8500 chipset support Intel’s virtualization technology, also known as Vanderpool. This technology allows the system to be divided (“partitioned”) into several independent machines.

- Pellston technology: This technology disables part of the memory cache that are giving too many ECC errors, for two reasons. First, speed. At each ECC error time is lost correcting the corrupted data. Secondly, if a memory area is giving too many ECC errors this probably means that it is not so good and can burn at any time soon.

- Foxton technology: Dynamic overclocking technology, if the processor requires an extra performance during load peaks. It is the first time we see a CPU manufacturer officially doing an overclocking technique.

[nextpage title=”Performance”]

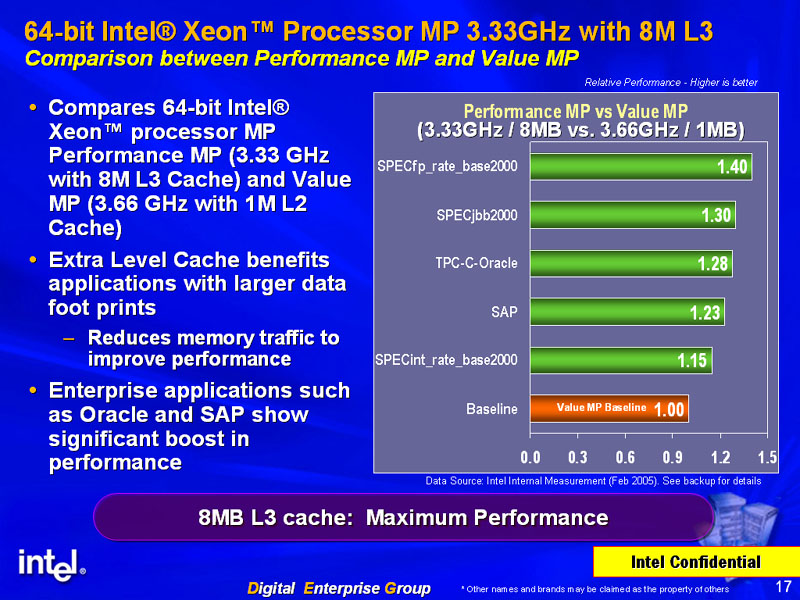

In Figure 1, you can see a chart provided by Intel comparing a 3.33 GHz 64-bit Xeon MP with 8 MB L3 memory cache performance with a 3.66 GHz 64-bit Xeon MP with just 1 MB L3 memory cache. As you can see, for applications that really need Xeon MP processors, like SAP and Oracle, it is better to have a bigger L3 memory cache than a higher clock rate.

Figure 1: 3.33 GHz 64-bit Xeon MP with 8 MB L3 memory cache vs. 3.66 GHz and 1 MB L3 memory cache.

Figure 1: 3.33 GHz 64-bit Xeon MP with 8 MB L3 memory cache vs. 3.66 GHz and 1 MB L3 memory cache.

Another advantage of this new Xeon MP model is its scalability. When we install more than one processor in a server, the server performance is not multiplied by the number of available processors. I.e., a system with two Xeon processors isn’t twice faster than a system with just one. According to Intel, the performance will increase between 1.59x and 1.92x, depending on the software used. In the case of four CPU configuration, the increase in performance varies between 2.14x and 3.52x, once again depending on the used software.

But with 64-bit Xeon MP the performance gain when we install more than one CPU is greater than the one obtained with the previous Xeon MP generation, reaching up to 3.96x in a system with four CPUs and up to 1.99x in a system with two CPUs, so with this processor the idea of the performance to be multiplied by the number of CPUs available is more likely. We show this in Figure 2.

Figure 2: Increase in performance due to the increase on the number of processors on the system.

[nextpage title=”Intel E8500 Chipset”]

Let’s talk now about the new Intel E8500 chipset and its new features.

This chipset has the following basic specs:

- PCI Express bus support (three 8x slots and one 4x slot).

- PCI-X bus support (one PCI-X 133 slot and two PCI-X 100 slots).

- Four memory channels, allowing a maximum theoretical transfer rate of 12,800 MB/s using DDR2-400 memories.

- DDR266, DDR333 and DDR2-400 memories support (pay attention because this chipset doesn’t support DDR400 memories but DDR2-400).

- Supports dual-core Xeon CPUs (code-named Paxville).

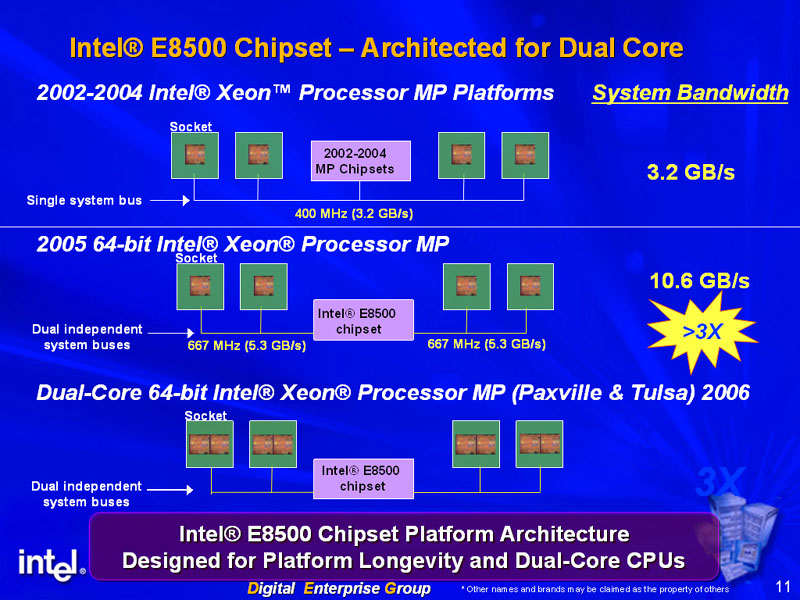

- Two independent busses. At the previous chipset for Xeon MP (Intel E8870) all system processors shared the same 400 MHz (3.2 GB/s) bus. In this chipset we have two independent busses of 667 MHz (5.3 GB/s) each, thus it is said that servers based on this CPU has an external maximum theoretical transfer rate of 10.6 GB/s. If two processors are used, each processor will be installed on a separated bus. If a four-CPU configuration is used, each bus will have two CPUs installed.

Figure 3: Intel E8500 chipset dual bus architecture.

Figure 3: Intel E8500 chipset dual bus architecture.

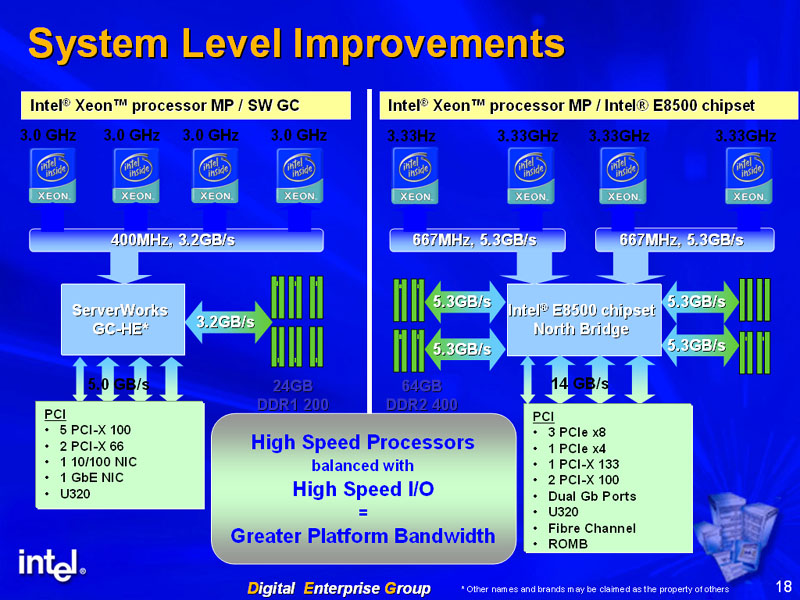

Figure 4: Intel E8500 chipset summary and comparison with a ServerWorks GC-HE chipset solution.

Figure 4: Intel E8500 chipset summary and comparison with a ServerWorks GC-HE chipset solution.

Leave a Reply